ESD Protection in PIC Testing is a top priority at VLC Photonics. We take pride in offering premier testing services for Photonic Integrated Circuits (PICs). Our facilities, certified to ISO Class 6 (Class 1,000), provide an optimal environment for rigorous testing processes. With a focus on maintaining the highest standards of quality, our clean room laboratories are equipped with the latest technology, and all tests are conducted by a team of highly skilled engineers.

Clean room laboratories

The testing of Photonic Integrated Circuits is a delicate process that demands a controlled environment to ensure the accuracy and reliability of results. Our clean room laboratories are certified as ISO Class 6, indicating that the number of airborne particles is strictly controlled to prevent contamination that could compromise the performance of the circuits. This certification ensures that our facilities maintain the cleanliness required for sensitive testing procedures.

Comprehensive ESD Protection in PIC Testing

A crucial aspect of our testing process is Electrostatic Discharge (ESD) protection. ESD is the sudden flow of electricity between two electrically charged objects, which can cause severe damage to sensitive electronic components, including Photonic Integrated Circuits. ESD protection in PIC Testing is vital to prevent any electrical overstress that could lead to circuit failure or performance degradation.

Principle of ESD protections in PIC Testing

It’s pretty basic physics – materials with different charges touching each other with different electric potentials create current. This can be air to tool, tool to chip, person to screwdriver, screwdriver to tool to assembly. Triboelectrification – two materials are charged when they are separated (rubbing, friction) due to the exchange of electrons to equalize electrochemical potential.

In some very extreme cases, a person can pass such charge to electrically grounded objects, this is probably the most known effect for general population. It must be said that such discharge where a person can feel a visible spark to car doors is usually 500 times more powerful than one which can destroy a photonic integrated chip.

Generated current from an ESD event follows basic principle of the path of least impedance. This means that designer can design a chip in the way that if ESD event occurs it is partially redirected/rerouted where designer wants – usually to grounding cable. Why partially? Because current follows Kirchoff’s current law, and it will be proportionally distributed between resistance paths.

ESD in the semiconductor industry

ESD related failures in the semiconductor industry (where PIC with active components such as modulators, detectors, and lasers belong to) are associated to >80% of failures in designs, processes, and production.

Every step in the semiconductor laboratory or process must be considered for ESD protection or prevention by securing the laboratory to the latest standards, ESD safe equipment with implemented safety features and component (device under fabrication or test) design to accommodate unwanted discharges. A combination of design features in devices to reduce damage threshold voltage and current combined with reduced static charge on tools, people and equipment allows to have a safe environment of ESD Protection in PIC Testing.

ESD consideration in PIC Testing and development

ESD process prevention starts with the device under fabrication or test process requirements. Build in features like capacitance to direct static charges occurring directly on to device can redirect unwanted voltage spikes from key components on the chip to grounding pins. Every building block on the circuit can have different damage thresholds for current and voltage, usually most sensitive blocks are the ones that work in high frequency with low capacitance, and small PN junction.

The care die can be designed in shunt transistors, good grounding design, and component placement design to reduce ESD damage to critical components. When a circuit is assembled to the package, more protection against current and voltage spikes can be implemented in means of grounding and electromagnetic wave protection which can induce unwanted currents on electrical contacts inside of the die. In many cases, this will be seen as electrical noise rather than electrical damage, but in other cases it can damage permanently the components on the chip.

Cleanroom facility for ESD protection in PIC Testing

When designing a clean room based on current, resistance, and voltage specifications, it is essential to consider grounding as a fundamental aspect. Grounding the building and all tools is the most crucial and straightforward solution. If everything is grounded to the same 0V potential, the primary focus should then be on ensuring that all remaining components, such as tools, people, furniture, have a path for current flow to ground. This will help equalize the entire clean room system, from personnel and devices to tools, air, and grounding cables.

There are two types of protective equipment for ESD: conductive and dissipative. Dissipative materials help reduce current by offering higher resistivity, making them suitable for slow discharge. In contrast, conductive protection directs low voltages through low-resistance materials, but it does not reduce current flow

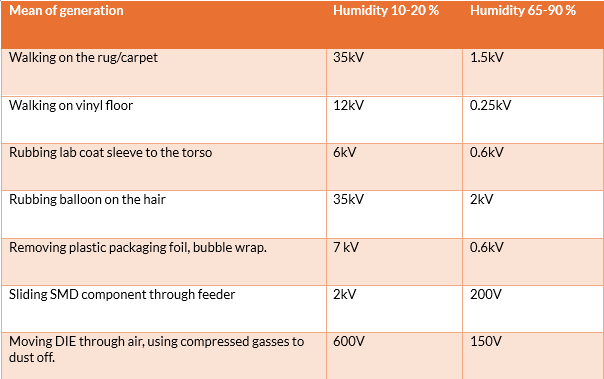

Humidity plays a critical role in ESD protection in PIC testing. Rigorous testing must be conducted across different environments where the device will be used. At low humidity levels of 10-20%, the voltage of static discharges can be 3-10 times higher than in a more humid environment of 65-90%. This is because humid air is more conductive, which helps reduce surface charges on materials, tools, and personnel.

Below is the table for typically encountered voltages from ESD events in the lab:

In Semiconductor and PIC laboratories and fabrication centers, humans are usually key generators of static discharges. The easiest way to maintain low potential on humans is to have a decapitating connection to the ground. This is usually done via mattress and/or bracelet. Both techniques are complementary and both work in the same principle. Bracelet has benefits if the personnel is sitting on chairs and feet don’t touch the ground, and mattress is better if the personnel walks around the workstation and may need to disconnect bracelet. There are some relevant standards such as DOD-HDBK-263 / MIL-STD-454.

Another important factor is the movement of tools, as friction between robotic components and air can generate significant static charge. One way to reduce this charge is by bombarding the tool with ionized air particles, which helps to equalize the charge to the average charge specified by the air ionizer.

Another important component is process design, especially related to grounding pins on the chips, tools, PCBs, and connections. It is very important to first connect and mount in every process grounding connector. This allows to have safety connected first before any other connections and manipulations to devices are done, no matter if it’s wire bonding process, picking process, package mounting process, or active test on characterization bench or wafer level test tool.

Potential damages due to the lack of ESD protection

Damage to electronic devices due to lack of ESD protection can be in two ways:

- • Catastrophic failure: basically your component combusts and evaporates.

- • Latent failures: more difficult to catch, as they can cause extremely small irregularities to components which can show up in weeks or even months. This is worst because qualified devices can break down on the customer site, incurring extreme costs for replacement and repairs.

At VLC Photonics, we have implemented vigorous design processes and comprehensive ESD protection measures in laboratories to safeguard against such risks. Our clean rooms are fully equipped with ESD-safe materials and tools, and our engineers follow strict protocols to minimize the potential for electrostatic discharge. These measures include grounding all equipment and personnel, using antistatic mats, wrist straps, and maintaining controlled humidity levels to reduce the build-up of static electricity.

VLC Photonics’ commitment to excellence in design and testing is reflected in our advanced facilities and meticulous attention to detail, particularly in the area of ESD protection. By providing a controlled environment and utilizing industry-leading practices, we ensure that the integrity and performance of your Photonic Integrated Circuits are preserved throughout the design and testing processes to provide best in class semiconductor devices in controlled environment. Trust VLC Photonics for reliable and precise testing services that meet the highest industry standards.

Did you enjoy this article about ESD Protection in PIC Testing?, don’t miss our insightful article PIC Testing House: Why is it key to test with one?